3DDE300416 提供足够的相位位来跟踪如此低的频率

自从我写了关于 AXI-Lite 的前两篇文章以来,第一篇讨论了如何验证 AXI-Lite 接口,第二篇讨论了如何构建 AXI-Lite 从器件,我不仅有机会构建一个 AXI-Lite,而且有机会构建多个 AXI-轻度奴隶。(1、 2、 3、 4、 5、 6等)很酷的部分是,我遇到了一些非常简单的方法来做到这一点,我认为可能值得分享。

在我们开始之前,一个警告:

如果您有兴趣以简单的方式构建 AXI-Lite 从设备, 请不要从供应商 IP 开始! 它坏了。 Xilinx 的 AXI-Lite 演示代码至少从 2016 年开始就被破解了。他们承诺在 2020 年进行修复,但我还没有看到。 英特尔的设计也有问题 (他们的论坛也是如此,否则我可能已经报告了错误)。

不,从正式的属性文件开始。从那里,您可以使用或不使用滑动缓冲器 ,您的选择取决于您希望从 AXI-lite 从器件获得的性能。不过,在这两种情况下,我们今天都将了解如何轻松构建 AXI-Lite 从设备。

|

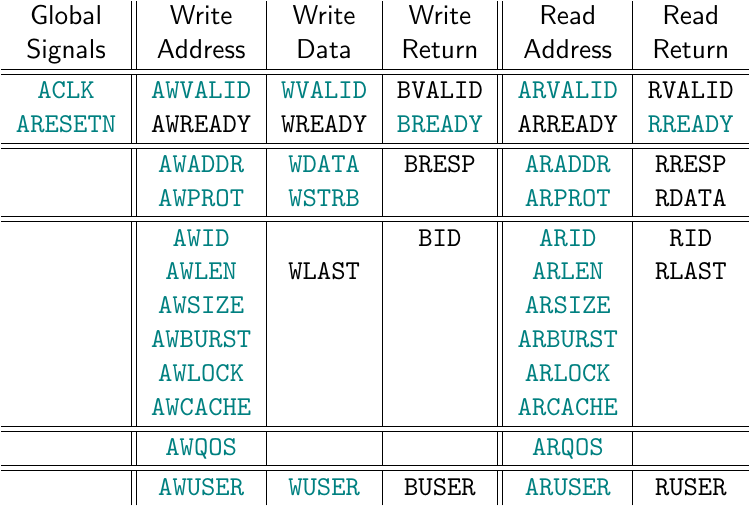

当您按照下面的说明进行操作时,请考虑显示右侧图 1 中显示的各种 AXI 信号名称的图表。该图表按通道组织成列:有信号前缀为的写地址通道AW、信号前缀为写数据通道W、信号前缀为写返回通道B、信号前缀为读地址通道AR和读返回通道信号前缀为R. 在我们下面的从机中,我们将遵循 Xilinx 的示例并添加额外的前缀S_AXI_。该图表的第一行显示了一对握手信号,*VALID并且 *READY,需要控制每个通道上的数据流。下一行显示了我们今天要处理的 AXI-Lite 信号。下面的三行显示了不属于 AXI- lite 协议的 AXI 信号。

我们的目标是控制一组内部寄存器到 我们的核心,同时还 通过图 1 中黑色所示的各种 AXI-Lite 信号回复总线

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。