3BSE018138R1 逻辑的问题只是吞吐量性能

让我们来看看我们如何处理传入的有效/就绪握手。具体来说,这包括如何处理S_AXI_AWREADY、S_AXI_WREADY和S_AXI_ARREADY。这些也是Xilinx 在构建演示内核时弄乱的信号 。界面

|

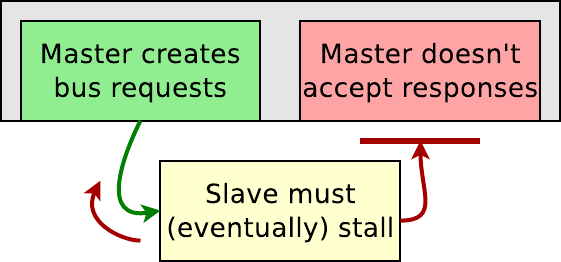

这些就绪信号的困难部分是背压。如果主人保持BREADY低位,奴隶必须知道降低AWREADY和 WREADY。如果主人保持RREADY低位也是如此,那么奴隶需要知道降低ARREADY。因为这些不是人们通常想到的情况,所以仅通过模拟进行测试时,这些信号很容易出错。这不是您在编写模拟脚本时可能会想到的情况。

一般来说,有两种方法来处理传入的通道——有和没有skid buffer s。使用skid buffer,你的 slave 将能够实现更低的延迟和更高的吞吐量。如果没有skid buffer,你的 slave 将有更少的逻辑和只有 50% 的吞吐量,但它仍然是一个有效的 AXI-Lite slave。

在本节中,我们将研究如何以简单的方式处理这些握手——不使用任何滑动缓冲区。

让我们再次从写入端开始。我们将在此处遵循(并修复)Xilinx 的示例,并且仅在和都 为真S_AXI_AWREADY时才引发。这会将两个通道同步在一起——这是任何 AXI 从设备的重要组成部分。S_AXI_AWVALIDS_AXI_WVALID

这个逻辑的初稿可能看起来像,

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。