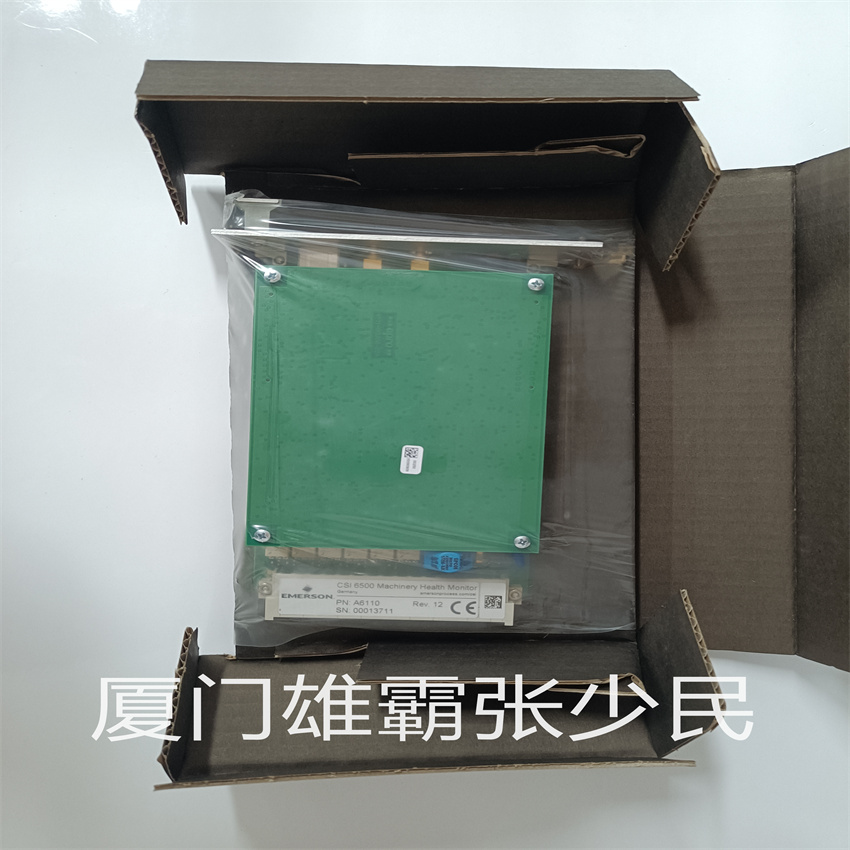

EMERSON A6824 组件用于印制电路板设计

一个半导体知识产权核心(SIP核心),IP核,或者IP块是可重用的逻辑单元、单元或集成电路布局设计是知识产权一方的。IP内核可以是得到许可的转让给另一方或由一方拥有和使用。该术语来自的许可专利的或者源代码版权存在于设计中。设计师专用集成电路(ASIC)和系统现场可编程门阵列(FPGA)逻辑可以使用IP内核作为构建模块。

历史[编辑]20世纪90年代,芯片设计中IP核的许可和使用成为普遍做法。[需要引用]有许多许可人,也有许多铸造厂在市场上竞争。2013年,获得最广泛许可的IP内核来自Arm控股公司(43.2%的市场份额),新思科技公司。(13.9%的市场份额),想象技术公司(9%的市场份额)和Cadence设计系统公司(5.1%的市场份额)。[1]

IP核的类型[编辑]IP核在芯片设计相当于使用图书馆为计算机编程或者是离散的集成电路组件用于印制电路板设计。每一个都是可重复使用的设计的组成逻辑使用定义的连接和行为已证实的并整合到一个更大的设计中。

软核[编辑]IP内核通常以下列形式提供可合成的 RTL在一个硬件描述语言诸如Verilog或者极高密度脂蛋白。这些类似于低级语言比如计算机编程领域的C。IP核心交付给芯片设计师因为RTL允许芯片设计者在功能级修改设计,尽管许多ip供应商不提供保证或者支持修改的设计。[需要引用]

IP核有时也作为通用门级提供网表。网表是作为类属实现的IP逻辑功能的布尔代数表示大门或者过程-具体标准细胞。实现为通用门的IP核可以针对任何工艺技术进行编译。门级网表类似于汇编码计算机编程领域的列表。网表为IP核心供应商提供了合理的保护,防止逆向工程。另请参见:集成电路布图设计保护。

网表和可综合内核都被称为软内核,因为它们都允许综合,放置和布线(心灵研究学会(Society for Psychical Research))设计流程。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。